LXF162:CPU своими руками

Olkol (обсуждение | вклад) |

Olkol (обсуждение | вклад) м (Olkol переименовал страницу LXF162:CPU своими руками,часть II 50 в LXF162:CPU своими руками) |

||

| (не показаны 12 промежуточных версий 1 участника) | |||

| Строка 29: | Строка 29: | ||

===Больше логики=== | ===Больше логики=== | ||

| − | [[Файл: LXF162.feat_cpu.figur_opt1.jpeg|left | | + | [[Файл: LXF162.feat_cpu.figur_opt1.jpeg|left|300px |thumb|Рис. 2. АЛУ, использующее мультиплексоры для обеспечения выбора между операциями.]] |

Чтобы это продемонстрировать, мы скомбинируем наш полный сумматор с прошлого раза с другими логическими схемами (AND, OR и XOR), и используем мультиплексор для указания операций, которые требуется выполнить. | Чтобы это продемонстрировать, мы скомбинируем наш полный сумматор с прошлого раза с другими логическими схемами (AND, OR и XOR), и используем мультиплексор для указания операций, которые требуется выполнить. | ||

| Строка 41: | Строка 41: | ||

Все это показано на рис. 2, хотя вы можете также загрузить схему с диска – ALU.circuit – и рассмотреть ее хорошенько. Важная подсказка: все должно быть выровнено, потому что начнется большая путаница, если биты одного и другого входов пойдут в разном порядке, а порядок выходных битов тоже окажется другим! | Все это показано на рис. 2, хотя вы можете также загрузить схему с диска – ALU.circuit – и рассмотреть ее хорошенько. Важная подсказка: все должно быть выровнено, потому что начнется большая путаница, если биты одного и другого входов пойдут в разном порядке, а порядок выходных битов тоже окажется другим! | ||

| + | {{Врезка|right|Заголовок= Другие полезные операции|Ширина=30%|Содержание= Мы использовали AND, OR и XOR как примеры операций для расширения нашего сумматора, потому что эти схемы просты в создании. Но если вы работаете с числами без знака, то логический сдвиг влево или вправо может оказаться более естественным выбором для расширения нашего сумматора. | ||

| + | |||

| + | Как и предполагает название, логический сдвиг влево сдвигает все биты на одну позицию влево, а логический сдвиг вправо – на одну позицию вправо. Бит, который выпадает, потерян навсегда, а свободное место, появившееся в начале, занимает 0. | ||

| + | |||

| + | Если число является беззнаковой переменной, эти операции имеют эффект умножения (сдвиг влево) или деления (сдвиг вправо) числа на два. Это должно быть очевидно, поскольку каждая позиция имеет вес в два раза больший, чем позиция справа от нее. }} | ||

Рассмотрев схему поближе, вы увидите рядом с адресными входами список значений, на которые они должны быть настроены для выбора разных операций. В настоящем компьютере это именуется opcodes (сокращение от «коды операций»). Их нужно передать процессору, чтобы заставить его выполнить определенное действие. Рядом с кодами находятся трехбуквенные описания функций – это мнемоника, для простоты запоминания и человеко-читаемого описания того, что делают разные коды. Если вы когда-нибудь писали на языке ассемблера, то это как раз и есть мнемонические значения, которые компиляторы ассемблера затем превращают в двоичные эквиваленты. | Рассмотрев схему поближе, вы увидите рядом с адресными входами список значений, на которые они должны быть настроены для выбора разных операций. В настоящем компьютере это именуется opcodes (сокращение от «коды операций»). Их нужно передать процессору, чтобы заставить его выполнить определенное действие. Рядом с кодами находятся трехбуквенные описания функций – это мнемоника, для простоты запоминания и человеко-читаемого описания того, что делают разные коды. Если вы когда-нибудь писали на языке ассемблера, то это как раз и есть мнемонические значения, которые компиляторы ассемблера затем превращают в двоичные эквиваленты. | ||

| Строка 53: | Строка 58: | ||

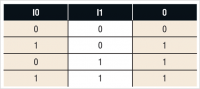

Возьмем обычный вентиль OR. Напомним его таблицу истинности: | Возьмем обычный вентиль OR. Напомним его таблицу истинности: | ||

| + | [[Файл:LXF162.feat_cpu.figure8.png |left |200px ]] | ||

| − | + | Вентиль OR будет гарантированно вести себя именно так, если только... Что произойдет, если подключить выход ко входу? Что если создать сигнал обратной связи? | |

| − | + | Посмотрите на схему на рис. 3 слева. Здесь вы видите, как мы ответвили выход и соединили его напрямую с одним из входов. Оставшийся вход по-прежнему присоединен к нашему логическому вентилю. | |

| − | + | Пока оставшийся вход – это 0, все устройство остается в этом состоянии. Однако стоит вам переключить вход на 1, как устройство заблокируется. Выход будет постоянно передавать 1 обратно на вход, и из этого состояния будет не выйти. Образно выражаясь, вентиль заперт. Попробуйте создать эту схему, чтобы понять, как она работает. | |

| − | + | ===Триггер задержки=== | |

| − | === | + | |

| − | В созданном нами триггере задержки вход действует, только когда переключатель enable установлен на 1. Это прекрасно, но в компьютерах и в цифровой электронике в целом удобны схемы, которые активируется за более короткое время, то есть пока вход enable переходит из одного состояния в другое. Это позволяет создавать намного более чувствительные схемы, с более тонким контролем над ними. Когда схемы, подобные триггеру задержки, запускаются во время переброса входа enable из 0 в 1, это называется уже не триггером, а мультивибратором. Мы говорим о «срабатывании по перепаду сигнала [edge triggering]». | + | Очевидно, что этой простой схемы обратной связи недостаточно для применения в качестве ячейки памяти – задав это состояние, вы не сможете переустановить его! Если вы записали туда порцию данных, а затем решили записать еще, то вам не повезло. Есть другие схемы, которые используют тот же принцип обратной связи, но без такого ограничения. Одна из них известна под названием «триггер D-типа» или триггер задержки, и мы его используем, чтобы продемонстрировать, как в компьютерах работает память. |

| + | |||

| + | Взгляните на схему в правой части рис. 3. Это промежуточный шаг между нашей простой схемой обратной связи и триггером задержки. Он известен под названием «закрытый триггер S-R» или триггер пересчета. Если в этой схеме оба входа установлены в нуль (zero), выходы остаются блокированными – иными словами, они помнят свое предыдущее состояние. Если верхний вход установлен в 1, то нижний выход будет 1; а если нижний вход равен 1, верхний выход равен 1. | ||

| + | [[Файл: LXF162.feat_cpu.figur_opt2.jpeg| |thumb|400px|Рис. 3. Схема обратной связи слева демонстрирует основной принцип цифровой памяти, а триггер пересчета справа показывает, как получить больший контроль над схемой.]] | ||

| + | |||

| + | Идея этой схемы в том, что два выхода всегда должны быть в противоположных состояниях. Однако так будет не всегда: если одновременно задать на оба входа 1, оба выхода станут равны 0. Эту ситуацию можно обойти, создав триггер задержки, который также дает нам большую степень контроля за операциями схемы. Один из них можно увидеть на рис. 4. | ||

| + | |||

| + | Самая важная функция в этой схеме на текущий момент в том, что, соединяя входы в единое управление и инвертируя его, мы обеспечиваем такую ситуацию, когда схема не может оказаться в нештатном положении. Второе, что стоит отметить, это использование вентиля AND для «перекрытия» схемы. Это обеспечивает второй вход, который должен быть переключен на 1, чтобы активировать схему. Когда она активируется, верхний выход будет всегда отражать вход, но когда она отключена, схема останется блокированной, что бы вы ни делали со входом. | ||

| + | |||

| + | Этот ввод часто именуют не Запуск [Enable], а Такты [Clock], и далее будет понятно, почему. Если не обращать внимания на нижний выход и сфокусироваться только на верхнем, вы увидите, что у нас получилась 1-битная ячейка памяти. Вы пишете 1 или 0, активируя тактовый сигнал, и затем задаете вход, чтобы он имел любую величину, которую вы хотите сохранить. Когда вы отключите такты, ячейка сохранит эту величину, и вы сможете считать ее с верхнего выхода. | ||

| + | |||

| + | Начиная с настоящего момента и далее, когда нам понадобятся триггеры задержки, мы будем использовать встроенное представление KTechLab. Вы найдете его в разделе Integrated Circuits, где оно именуется “D Flip-Flop [мультивибратор]”. Они почти идентичны, но все же обязательно прочитайте раздел Запускающий перепад сигнала, чтобы понять разницу между триггером задержки и D Flip-Flop. | ||

| + | |||

| + | ===Применим результаты=== | ||

| + | |||

| + | Мы можем легко интегрировать эту память в созданное нами АЛУ, заменив индикаторы вывода триггерами задержки – по одному на каждый переключатель. Тогда память сможет запомнить результаты последнего вычисления. Вроде и не слишком полезно, но зато дает возможность соединить разные операции в нашем АЛУ, используя т. н. регистр-сумматор. | ||

| + | {{Врезка|left|Заголовок= Срабатывание по перепаду сигнала|Ширина=98%|Содержание=В созданном нами триггере задержки вход действует, только когда переключатель enable установлен на 1. Это прекрасно, но в компьютерах и в цифровой электронике в целом удобны схемы, которые активируется за более короткое время, то есть пока вход enable переходит из одного состояния в другое. Это позволяет создавать намного более чувствительные схемы, с более тонким контролем над ними. Когда схемы, подобные триггеру задержки, запускаются во время переброса входа enable из 0 в 1, это называется уже не триггером, а мультивибратором. Мы говорим о «срабатывании по перепаду сигнала [edge triggering]». | ||

Быть может, это звучит чуть ли не мистически, но если вы представите себе график прямоугольной волны, все станет ясно. Когда линия высоко, то вход или выход равны 1; когда она низко, это 0. В случае с триггером задержки выходы повторяют входы все время, пока enable высоко. В случае с мультивибратором, он будет реагировать только на одно ребро прямоугольного графика, образованного тогда, когда вход enable переходит в соcтояние 1. | Быть может, это звучит чуть ли не мистически, но если вы представите себе график прямоугольной волны, все станет ясно. Когда линия высоко, то вход или выход равны 1; когда она низко, это 0. В случае с триггером задержки выходы повторяют входы все время, пока enable высоко. В случае с мультивибратором, он будет реагировать только на одно ребро прямоугольного графика, образованного тогда, когда вход enable переходит в соcтояние 1. | ||

Это не просто интересно, поскольку при работе со встроенным D Flip-Flop от KTechlab вам нужно обеспечить включение и выключение тактового сигнала, чтобы он действовал. Он срабатывает при переходе от высокого уровня к низкому, так что вам нужно установить переключатель на 1 и снова на 0, чтобы активировать мультивибратор и заставить его сохранить новую величину. | Это не просто интересно, поскольку при работе со встроенным D Flip-Flop от KTechlab вам нужно обеспечить включение и выключение тактового сигнала, чтобы он действовал. Он срабатывает при переходе от высокого уровня к низкому, так что вам нужно установить переключатель на 1 и снова на 0, чтобы активировать мультивибратор и заставить его сохранить новую величину. | ||

| + | }} | ||

| + | [[Файл: LXF162.feat_cpu.figur_opt3.jpeg| |thumb|400px|> Рис. 4. Триггер D-типа работает как 1-битная схема памяти, решая проблемы с закрытым фиксатором SR. Под основной схемой располагается презентация встроенного D FlipFLop от KTechlab.]] | ||

| + | Чтобы это сделать, придется подвергнуть ранее созданное нами АЛУ некоторому редизайну. Его результаты показаны на рис. 5. Принципы почти те же: между входами и выходами по-прежнему существуют мультиплексоры, чтобы осуществлять выбор между разными операциями, и имеется набор кодов операций на выбор. Однако многое и изменилось. Самое важное, что мы интегрировали триггеры задержки в вывод, чтобы схема могла запомнить предыдущий результат. Это и есть регистр. | ||

| + | |||

| + | Суть регистра в том, что это как бы электронный блокнот – место, куда заносятся числа для дальнейшей обработки. Это ускоряет сложные операции, поскольку избавляет процессор от необходимости записывать промежуточные результаты в память и затем загружать их снова, чтобы выполнить операцию. | ||

| + | |||

| + | Это становится возможным благодаря использованию выхода регистра в качестве одного из входов, так что в оставшейся части схемы содержится только один набор переключателей входа, а остальные входы поступают с выхода регистра. | ||

| + | |||

| + | [[Файл:LXF162.feat_cpu.figure5_opt.png |left |400px |thumb| Рис. 5. Наше законченное АЛУ демонстрирует, как можно интегрировать схему памяти в процессор.]] | ||

| + | |||

| + | ===Новые команды=== | ||

| + | |||

| + | Имеется также несколько новых инструкций-команд, включая логический сдвиг влево и вправо (реализуемый простым соединением выхода регистра непосредственно со входами мультиплексоров, смещенными на одну позицию влево или вправо). | ||

| + | |||

| + | Также имеется команда LOD, или load, которая вводит первое число для обработки в регистр. И. наконец, вы также можете обратить внимание, что мы соединили Rst на каждом триггере с переключателем, чтобы можно было переключить состояние регистра в полный 0 одним нажатием. | ||

| + | |||

| + | Переключатель clock является эквивалентом enable в ранее созданном нами триггере задержки, но обязательно прочтите врезку «Срабатывание по перепаду сигнала», чтобы понять, как это работает. | ||

| + | |||

| + | Создав такую схему, вы можете загрузить число в регистр, ввести другое число на остальные входные переключатели, выбрать операцию переключателями opcode, а затем включить переключатель clock и выполнить операцию над содержимым регистра – если это команда ADD, то и над содержимым переключателей ввода (операции LSL и LSR обрабатывают только содержимое регистра). Если вы затем захотите выполнить другую операцию с результатом, то и такое будет возможно. | ||

| + | |||

| + | Вот и все, что мы собирались рассмотреть в статье этого месяца. Теперь у вас должно быть встроенное АЛУ с возможностью выполнения разных операций, как определено в специальных opcodes, способных соединить эти операции благодаря вводу регистра. | ||

| + | |||

| + | Нам предстоит еще долгий путь. В следующем выпуске мы рассмотрим, как интегрировать в процессор ОЗУ, соединив его с устройством управления, и ввести в ОЗУ программу, чтобы процессор выполнил всю серию команд. | | ||

| + | |||

| + | {{Врезка|right|Заголовок=Больше, больше, больше |Ширина=98%|Содержание= С триггерами задержки можно сделать еще и не то – возможно, самым важным будет возможность создать разновидность оперативной памяти(ОЗУ). Суть ОЗУ в соединении серии 1‑битных схем хранения, в нашем случае – триггеров задержки, таким образом, чтобы вы при желании могли читать или записывать определенные биты, находящиеся на хранении. Большинство ОЗУ не обладает структурой, позволяющей читать и записывать отдельные биты: они структурированы скорее для чтения и записи групп битов, размер которых в процессоре известен как длина слова.Большинство современных компьютеров работают с длиной слова, которая равна 32 или 64 битам. В нашем процессоре длиной слова выбрана величина 4 бита. | ||

| + | Решив создать собственную схему ОЗУ, вы, очевидно, сможете это сделать, руководствуясь накопленными знаниями. Вам нужно будет обеспечить возможность адресоваться к каждому слову в памяти – отличным решением станет декодер – и обдумать, как обращаться к каждому слову в памяти без | ||

| + | необходимости записывать значения вводимых битов, а также изобрести способ читать отдельное слово. | ||

| + | Здесь мог бы пригодиться вентиль AND. И, наконец, вам понадобятся некоторые входные биты, чтобы устанавливать значения внутри памяти, и выходные биты, чтобы проверять содержимое слова, к которому вы обращаетесь.}} | ||

Текущая версия на 12:58, 13 октября 2018

|

|

|

Содержание |

[править] CPU своими руками

Часть вторая

Еще два компонента электронного сердца вашего CPU: Джонатан Робертс подводит вас на шаг ближе к рабочему процессору.

В LXF158 мы показали вам, как построить собственный компьютер из базовых электронных блоков. По сути, мы изготовили двоичный сумматор. Мы закончили статью, сказав, что созданное нами — это еще далеко не настоящий компьютер, и вам нужны еще несколько компонентов, прежде чем ваша машина сможет претендовать на звание компьютера.

В этой статье мы рассмотрим дальнейшие шаги и представим вам еще несколько компонентов, продемонстрировав, как расширить возможности вашего сумматора до выполнения других действий (AND [И], XOR [ИСКЛ.ИЛИ] и NOT [ИЛИ]) и создать цепи памяти для хранения ввода и вывода.

Перед чтением этой статьи вам стоит прочесть предыдущую часть, чтобы освежить память, поскольку мы исходим из того, что вы с ней ознакомлены. Если у вас нет экземпляра LXF158, вы сможете найти PDF этой статьи на диске этого месяца.

[править] Декодер

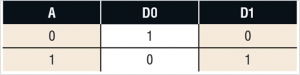

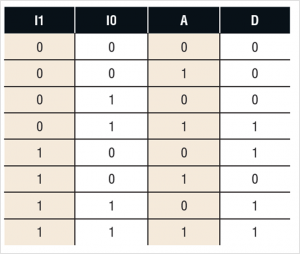

Первый компонент, который мы рассмотрим – это декодер, или, точнее, линейный декодер. Он очень прост, но очень удобен в работе и сам по себе, и декодеры также используются в мультиплексорах – что исключительно важно для остальной части нашей статьи.

По сути, все декодеры позволяют сделать выбор из множества выходов, используя только половину входов. Более конкретно – при единственном входе декодер позволит вам выбирать между двумя выходами, два входа обеспечат вам выбор из четырех выходов, и т. д. В случае декодеров мы говорим не о входе и выходе, а об адресной линии и линии передачи данных. Таблица истинности для простого линейного декодера 1-в-2 размещена ниже, а схема соединений приведена на рис. 1.

Как видите, все очень просто. Адресная линия раздвоена, и вход NOT размещен на одном ответвлении этого раздвоения. Таким образом, только одна из этих линий передачи данных может за один раз передать 1.

[править] Мультиплексоры

Мультиплексор подобен декодеру, но способен на большее. Вместо выбора между двумя линиями передачи данных, он использует адресную линию для выбора между двумя входами, и выбранная величина (0 или 1) будет перенаправлена на единственную линию передачи данных.

Его таблица истинности приведена ниже, а его схему соединений вы также можете увидеть на рис. 1. На этой схеме вы видите, что мультиплексор – это просто расширенный декодер.

[править] Больше логики

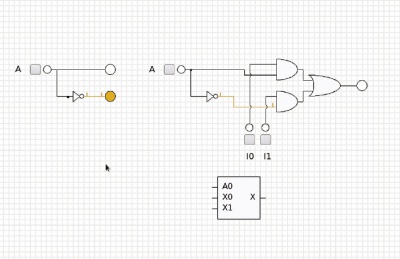

Чтобы это продемонстрировать, мы скомбинируем наш полный сумматор с прошлого раза с другими логическими схемами (AND, OR и XOR), и используем мультиплексор для указания операций, которые требуется выполнить.

Первое, что нужно сделать – создать логическую схему. Это просто, поскольку, чтобы выполнить AND для двух двоичных чисел, все, что вам нужно сделать – это соединить каждый из первых битов с входом AND, вторые биты – с другим, третьи – с другим, и так далее. То же верно и для операций OR и XOR. Пока что можете оставить выходы несоединенными.

Присмотревшись внимательнее, вы сможете увидеть все это на рис. 2. Однако помните, что KTechlab не очень хорошо работает со сложными схемами, подобными этой, и будьте внимательны, рисуя соединения – проще всего будет перевести это в режим Manual, выбрав нужную опцию под значком с красной ручкой.

Сделав это, создайте четыре мультиплексора, настроив длину адреса каждого на два. Это можно сделать, щелкнув по мультиплексору, затем заглянув в появившуюся панель справа (Item Editor). Получится мультиплексор с четырьмя входами, между которыми вы сможете выбирать, создавая разные комбинации двух адресных линий.

Далее, соедините первый вход AND, вход OR, вход XOR и сумматор с первым мультиплексором, второй вход – со вторым мультиплексором, и так далее. Затем соедините логические выводы с соединением мультиплексора, отмеченным x, и, наконец, присоедините еще два логических ввода: один – ко всем A0, и другой – ко всем A1 на мультиплексорах.

Все это показано на рис. 2, хотя вы можете также загрузить схему с диска – ALU.circuit – и рассмотреть ее хорошенько. Важная подсказка: все должно быть выровнено, потому что начнется большая путаница, если биты одного и другого входов пойдут в разном порядке, а порядок выходных битов тоже окажется другим!

- Метамодернизм в позднем творчестве В.Г. Сорокина

- ЛитРПГ - последняя отрыжка постмодерна

- "Ричард III и семиотика"

- 3D-визуализация обложки Ridero создаем обложку книги при работе над самиздатом.

- Архитектура метамодерна - говоря о современном искусстве, невозможно не поговорить об архитектуре. В данной статье будет отмечено несколько интересных принципов, характерных для построек "новой волны", столь притягательных и скандальных.

- Литература

- Метамодерн

- Рокер-Прометей против изначального зла в «Песне про советскую милицию» Вени Дркина, Автор: Нина Ищенко, к.ф.н, член Союза Писателей ЛНР - перепубликация из журнала "Топос".

- Как избавиться от комаров? Лучшие типы ловушек.

- Что делать если роблокс вылетает на windows

- Что делать, если ребенок смотрит порно?

- Почему собака прыгает на людей при встрече?

- Какое масло лить в Задний дифференциал (мост) Visco diff 38434AA050

- О чем может рассказать хвост вашей кошки?

- Верветки

- Отчетность бюджетных учреждений при закупках по Закону № 223-ФЗ

- Срок исковой давности как правильно рассчитать

- Дмитрий Патрушев минсельхоз будет ли преемником Путина

- Кто такой Владислав Поздняков? Что такое "Мужское Государство" и почему его признали экстремистским в России?

- Как правильно выбрать машинное масло в Димитровграде?

- Как стать богатым и знаменитым в России?

- Почему фильм "Пипец" (Kick-Ass) стал популярен по всему миру?

- Как стать мудрецом?

- Как правильно установить FreeBSD

- Как стать таким как Путин?

- Где лучше жить - в Димитровграде или в Ульяновске?

- Почему город Димитровград так называется?

- Что такое метамодерн?

- ВАЖНО! Временное ограничение движения автотранспортных средств в Димитровграде

- Тарифы на электроэнергию для майнеров предложено повысить

Рассмотрев схему поближе, вы увидите рядом с адресными входами список значений, на которые они должны быть настроены для выбора разных операций. В настоящем компьютере это именуется opcodes (сокращение от «коды операций»). Их нужно передать процессору, чтобы заставить его выполнить определенное действие. Рядом с кодами находятся трехбуквенные описания функций – это мнемоника, для простоты запоминания и человеко-читаемого описания того, что делают разные коды. Если вы когда-нибудь писали на языке ассемблера, то это как раз и есть мнемонические значения, которые компиляторы ассемблера затем превращают в двоичные эквиваленты.

Вот таким образом и создается схема, которую можно проинструктировать на выполнение всяких операций. Однако на данный момент ввод в эту схему осуществляется непосредственно нами – мы вручную настраиваем логический вход, а выход являет собой логические выводы, которые включаются и выключаются.

А если мы хотим, чтобы выход не просто исчезал, но превращался во вход следующего устройства? Или если мы хотим запрограммировать входы заранее?

[править] Обратная связь

Чтобы это сделать, нам нужна память, и именно это станет предметом остальной части нашей статьи. Но прежде чем перейти к схемам памяти, начнем с рассмотрения понятия обратной связи, которая лежит в основе схем памяти.

Возьмем обычный вентиль OR. Напомним его таблицу истинности:

Вентиль OR будет гарантированно вести себя именно так, если только... Что произойдет, если подключить выход ко входу? Что если создать сигнал обратной связи?

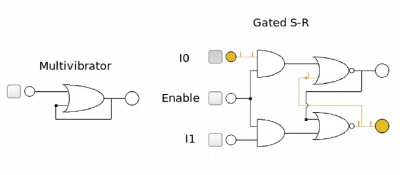

Посмотрите на схему на рис. 3 слева. Здесь вы видите, как мы ответвили выход и соединили его напрямую с одним из входов. Оставшийся вход по-прежнему присоединен к нашему логическому вентилю.

Пока оставшийся вход – это 0, все устройство остается в этом состоянии. Однако стоит вам переключить вход на 1, как устройство заблокируется. Выход будет постоянно передавать 1 обратно на вход, и из этого состояния будет не выйти. Образно выражаясь, вентиль заперт. Попробуйте создать эту схему, чтобы понять, как она работает.

[править] Триггер задержки

Очевидно, что этой простой схемы обратной связи недостаточно для применения в качестве ячейки памяти – задав это состояние, вы не сможете переустановить его! Если вы записали туда порцию данных, а затем решили записать еще, то вам не повезло. Есть другие схемы, которые используют тот же принцип обратной связи, но без такого ограничения. Одна из них известна под названием «триггер D-типа» или триггер задержки, и мы его используем, чтобы продемонстрировать, как в компьютерах работает память.

Взгляните на схему в правой части рис. 3. Это промежуточный шаг между нашей простой схемой обратной связи и триггером задержки. Он известен под названием «закрытый триггер S-R» или триггер пересчета. Если в этой схеме оба входа установлены в нуль (zero), выходы остаются блокированными – иными словами, они помнят свое предыдущее состояние. Если верхний вход установлен в 1, то нижний выход будет 1; а если нижний вход равен 1, верхний выход равен 1.

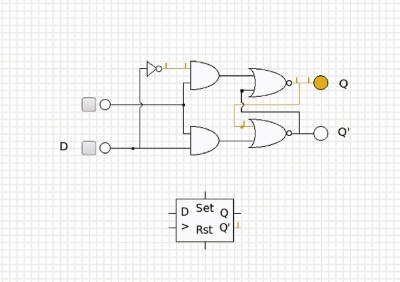

Идея этой схемы в том, что два выхода всегда должны быть в противоположных состояниях. Однако так будет не всегда: если одновременно задать на оба входа 1, оба выхода станут равны 0. Эту ситуацию можно обойти, создав триггер задержки, который также дает нам большую степень контроля за операциями схемы. Один из них можно увидеть на рис. 4.

Самая важная функция в этой схеме на текущий момент в том, что, соединяя входы в единое управление и инвертируя его, мы обеспечиваем такую ситуацию, когда схема не может оказаться в нештатном положении. Второе, что стоит отметить, это использование вентиля AND для «перекрытия» схемы. Это обеспечивает второй вход, который должен быть переключен на 1, чтобы активировать схему. Когда она активируется, верхний выход будет всегда отражать вход, но когда она отключена, схема останется блокированной, что бы вы ни делали со входом.

Этот ввод часто именуют не Запуск [Enable], а Такты [Clock], и далее будет понятно, почему. Если не обращать внимания на нижний выход и сфокусироваться только на верхнем, вы увидите, что у нас получилась 1-битная ячейка памяти. Вы пишете 1 или 0, активируя тактовый сигнал, и затем задаете вход, чтобы он имел любую величину, которую вы хотите сохранить. Когда вы отключите такты, ячейка сохранит эту величину, и вы сможете считать ее с верхнего выхода.

Начиная с настоящего момента и далее, когда нам понадобятся триггеры задержки, мы будем использовать встроенное представление KTechLab. Вы найдете его в разделе Integrated Circuits, где оно именуется “D Flip-Flop [мультивибратор]”. Они почти идентичны, но все же обязательно прочитайте раздел Запускающий перепад сигнала, чтобы понять разницу между триггером задержки и D Flip-Flop.

[править] Применим результаты

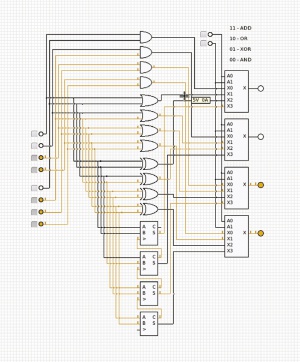

Мы можем легко интегрировать эту память в созданное нами АЛУ, заменив индикаторы вывода триггерами задержки – по одному на каждый переключатель. Тогда память сможет запомнить результаты последнего вычисления. Вроде и не слишком полезно, но зато дает возможность соединить разные операции в нашем АЛУ, используя т. н. регистр-сумматор.

- Метамодернизм в позднем творчестве В.Г. Сорокина

- ЛитРПГ - последняя отрыжка постмодерна

- "Ричард III и семиотика"

- 3D-визуализация обложки Ridero создаем обложку книги при работе над самиздатом.

- Архитектура метамодерна - говоря о современном искусстве, невозможно не поговорить об архитектуре. В данной статье будет отмечено несколько интересных принципов, характерных для построек "новой волны", столь притягательных и скандальных.

- Литература

- Метамодерн

- Рокер-Прометей против изначального зла в «Песне про советскую милицию» Вени Дркина, Автор: Нина Ищенко, к.ф.н, член Союза Писателей ЛНР - перепубликация из журнала "Топос".

- Как избавиться от комаров? Лучшие типы ловушек.

- Что делать если роблокс вылетает на windows

- Что делать, если ребенок смотрит порно?

- Почему собака прыгает на людей при встрече?

- Какое масло лить в Задний дифференциал (мост) Visco diff 38434AA050

- О чем может рассказать хвост вашей кошки?

- Верветки

- Отчетность бюджетных учреждений при закупках по Закону № 223-ФЗ

- Срок исковой давности как правильно рассчитать

- Дмитрий Патрушев минсельхоз будет ли преемником Путина

- Кто такой Владислав Поздняков? Что такое "Мужское Государство" и почему его признали экстремистским в России?

- Как правильно выбрать машинное масло в Димитровграде?

- Как стать богатым и знаменитым в России?

- Почему фильм "Пипец" (Kick-Ass) стал популярен по всему миру?

- Как стать мудрецом?

- Как правильно установить FreeBSD

- Как стать таким как Путин?

- Где лучше жить - в Димитровграде или в Ульяновске?

- Почему город Димитровград так называется?

- Что такое метамодерн?

- ВАЖНО! Временное ограничение движения автотранспортных средств в Димитровграде

- Тарифы на электроэнергию для майнеров предложено повысить

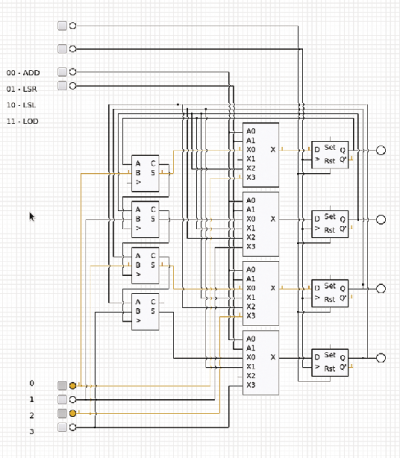

Чтобы это сделать, придется подвергнуть ранее созданное нами АЛУ некоторому редизайну. Его результаты показаны на рис. 5. Принципы почти те же: между входами и выходами по-прежнему существуют мультиплексоры, чтобы осуществлять выбор между разными операциями, и имеется набор кодов операций на выбор. Однако многое и изменилось. Самое важное, что мы интегрировали триггеры задержки в вывод, чтобы схема могла запомнить предыдущий результат. Это и есть регистр.

Суть регистра в том, что это как бы электронный блокнот – место, куда заносятся числа для дальнейшей обработки. Это ускоряет сложные операции, поскольку избавляет процессор от необходимости записывать промежуточные результаты в память и затем загружать их снова, чтобы выполнить операцию.

Это становится возможным благодаря использованию выхода регистра в качестве одного из входов, так что в оставшейся части схемы содержится только один набор переключателей входа, а остальные входы поступают с выхода регистра.

[править] Новые команды

Имеется также несколько новых инструкций-команд, включая логический сдвиг влево и вправо (реализуемый простым соединением выхода регистра непосредственно со входами мультиплексоров, смещенными на одну позицию влево или вправо).

Также имеется команда LOD, или load, которая вводит первое число для обработки в регистр. И. наконец, вы также можете обратить внимание, что мы соединили Rst на каждом триггере с переключателем, чтобы можно было переключить состояние регистра в полный 0 одним нажатием.

Переключатель clock является эквивалентом enable в ранее созданном нами триггере задержки, но обязательно прочтите врезку «Срабатывание по перепаду сигнала», чтобы понять, как это работает.

Создав такую схему, вы можете загрузить число в регистр, ввести другое число на остальные входные переключатели, выбрать операцию переключателями opcode, а затем включить переключатель clock и выполнить операцию над содержимым регистра – если это команда ADD, то и над содержимым переключателей ввода (операции LSL и LSR обрабатывают только содержимое регистра). Если вы затем захотите выполнить другую операцию с результатом, то и такое будет возможно.

Вот и все, что мы собирались рассмотреть в статье этого месяца. Теперь у вас должно быть встроенное АЛУ с возможностью выполнения разных операций, как определено в специальных opcodes, способных соединить эти операции благодаря вводу регистра.

Нам предстоит еще долгий путь. В следующем выпуске мы рассмотрим, как интегрировать в процессор ОЗУ, соединив его с устройством управления, и ввести в ОЗУ программу, чтобы процессор выполнил всю серию команд. |

- Метамодернизм в позднем творчестве В.Г. Сорокина

- ЛитРПГ - последняя отрыжка постмодерна

- "Ричард III и семиотика"

- 3D-визуализация обложки Ridero создаем обложку книги при работе над самиздатом.

- Архитектура метамодерна - говоря о современном искусстве, невозможно не поговорить об архитектуре. В данной статье будет отмечено несколько интересных принципов, характерных для построек "новой волны", столь притягательных и скандальных.

- Литература

- Метамодерн

- Рокер-Прометей против изначального зла в «Песне про советскую милицию» Вени Дркина, Автор: Нина Ищенко, к.ф.н, член Союза Писателей ЛНР - перепубликация из журнала "Топос".

- Как избавиться от комаров? Лучшие типы ловушек.

- Что делать если роблокс вылетает на windows

- Что делать, если ребенок смотрит порно?

- Почему собака прыгает на людей при встрече?

- Какое масло лить в Задний дифференциал (мост) Visco diff 38434AA050

- О чем может рассказать хвост вашей кошки?

- Верветки

- Отчетность бюджетных учреждений при закупках по Закону № 223-ФЗ

- Срок исковой давности как правильно рассчитать

- Дмитрий Патрушев минсельхоз будет ли преемником Путина

- Кто такой Владислав Поздняков? Что такое "Мужское Государство" и почему его признали экстремистским в России?

- Как правильно выбрать машинное масло в Димитровграде?

- Как стать богатым и знаменитым в России?

- Почему фильм "Пипец" (Kick-Ass) стал популярен по всему миру?

- Как стать мудрецом?

- Как правильно установить FreeBSD

- Как стать таким как Путин?

- Где лучше жить - в Димитровграде или в Ульяновске?

- Почему город Димитровград так называется?

- Что такое метамодерн?

- ВАЖНО! Временное ограничение движения автотранспортных средств в Димитровграде

- Тарифы на электроэнергию для майнеров предложено повысить